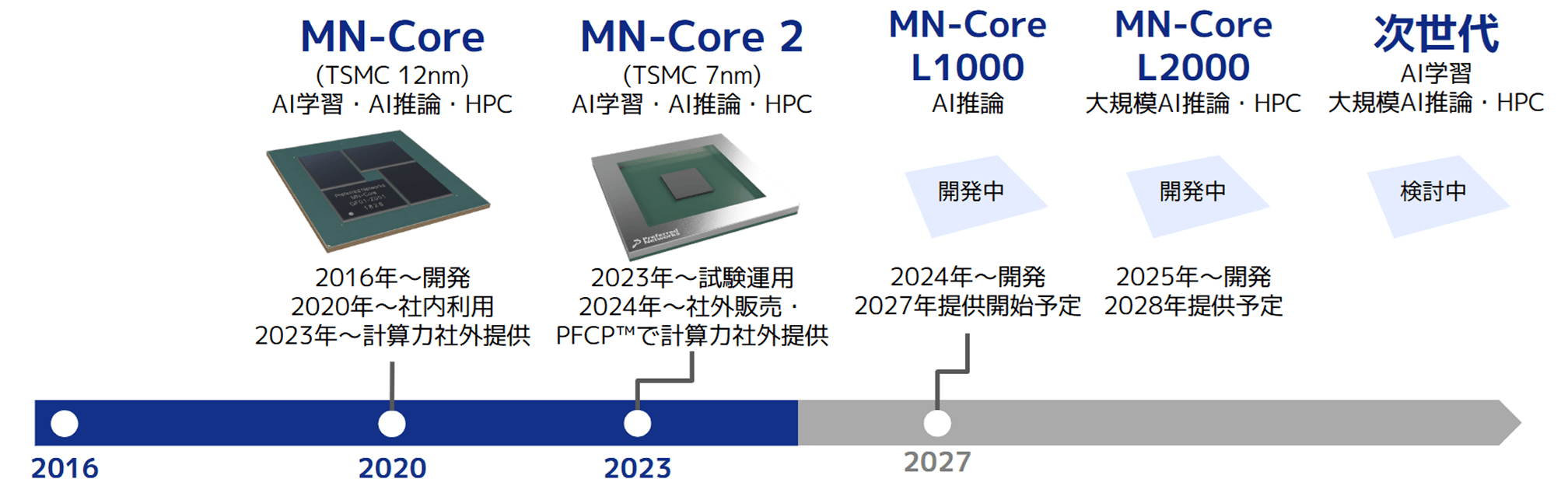

AIの開発や活用は現在、汎用GPUに大きく依存していますが、生成AIの急速な拡大により性能・コスト・消費電力・流通などがボトルネックとなっています。AIが社会実装され進化を続けるには、AIの計算処理に最適化された専用の半導体(チップ)の開発が不可欠です。PFNは創業間もない2016年からこの需要を見据え、AIの学習・推論を高速かつ高効率に処理するAI専用プロセッサー「MN-Core™」シリーズを神戸大学と共同で開発しています。MN-Coreシリーズは、汎用GPUと全く異なる設計思想にもとづき、AIに必要な計算処理に機能を限定することで、高い処理性能を発揮することができます。

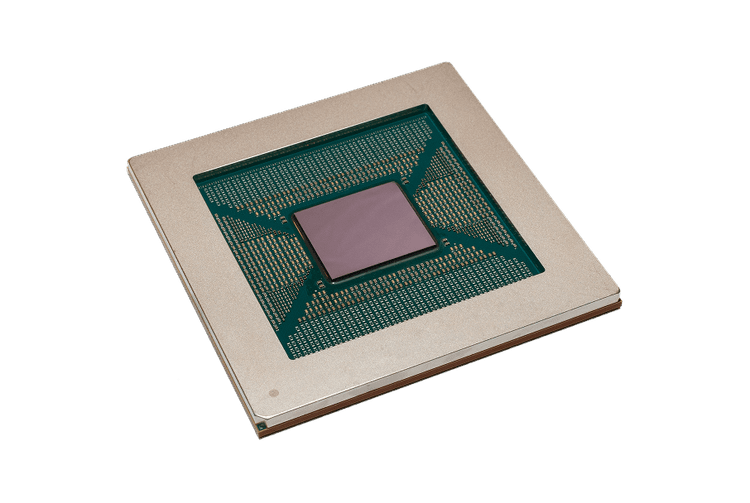

MN-Core Lシリーズの第1弾として開発中のMN-Core L1000は、生成AIの利用(推論処理)に特化したプロセッサーです。データを保存するメモリ(記憶装置)と演算器(ロジック)を従来のプロセッサーのように横に並べるのではなく垂直方向に積載する三次元積層構造にすることで、従来のハイエンドGPUに搭載されているHBM (high bandwidth memory)と比べてメモリ帯域幅(転送できるデータ量)を多く確保します。また、近年AIプロセッサーで利用が広がるSRAM(static random access memory)に比べて大容量かつ安価なDRAMを採用し、メモリの大容量化と高速化を安価に実現します。これにより、生成AI利用時(推論)の1秒あたりのトークン数を増やすことが可能になり、GPUなどの既存プロセッサーの最大10倍の高速処理を実現します。

MN-Core第2世代となるMN-Core 2は、第一世代のMN-Coreの電力あたり性能を維持しつつ、チップサイズを1/5以下に小型化し、設置面積あたりの計算能力を向上させたことで量産コストの低下を実現しました。

| MN-Core 2 | MN-Core 2(電力効率) | |

|---|---|---|

| FP64 | 12 TFlops | 37.24 GFlops/W |

| FP32 | 49 TFlops | 148.9 GFLops/W |

| TF32 | 98 TFlops | 297.9 GFlops/W |

| TF16 | 393 TFlops | 1,192 GFlops/W |

MN-Core 2ボードを8枚搭載するラックマウント型5Uサーバー。

MN-Core 2ボードを1枚搭載するデスクトップマシン。オフィス環境でも手軽に置くことが出来、MN-Core 2によるAIアクセラレーションを手軽に体感することが出来ます。

※MN-Core 2 Devkit 基本セットの設置場所は日本国内に限ります

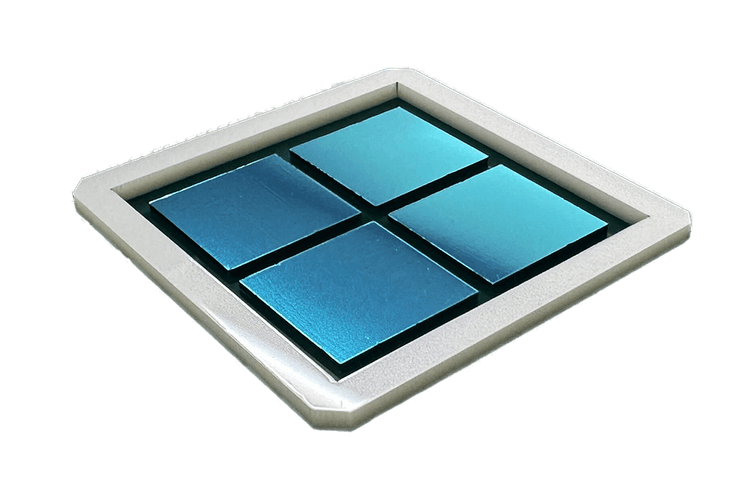

MN-Core第1世代は4ダイ1パッケージで構成されており、ダイにつき512個、計2048個の行列演算ブロックが集積されています。TSMC 12nmプロセスで製造されたMN-Core第1世代プロセッサーは、同一プロセスを採用する他のアクセラレーターに対して非常に高いピーク性能及び、電力当たり性能を実現します。

PFNではMN-Coreの第1世代プロセッサーを全体で160基使用し、それらを専用のインタコネクトを介して相互接続した計算基盤であるMN-3を2020年に構築し、運用しています。MN-3は世界のスーパコンピュータ電力効率ランキングであるGreen500において、2020年、2021年に世界1位を3回獲得し、その極めて高い省電力性能を実証しています。

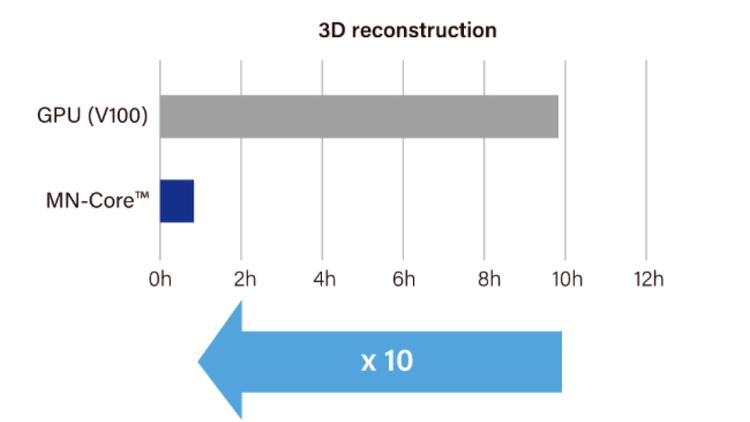

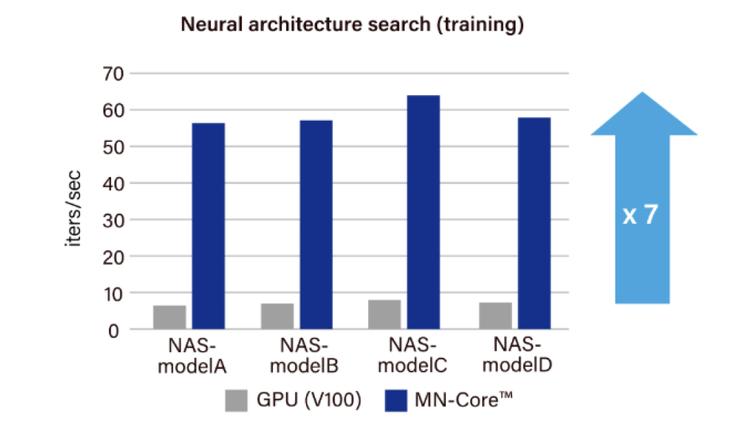

高い省電力性と高いピーク性能を両立するMN-Coreシリーズを用いることで、様々な実際のAIワークロードにおいてGPUに対しての高速化を実証しています。

PFN 3D Scanにおけるモデルの再構成処理を10倍程度高速化、数千のオブジェクトのスキャンに活用(MN-Core第1世代)

自律搬送ロボット「カチャカ」向け画像認識モデル探索において、精度と処理速度を両立するモデル候補を従来比約7倍の速度で発見(MN-Core第1世代)

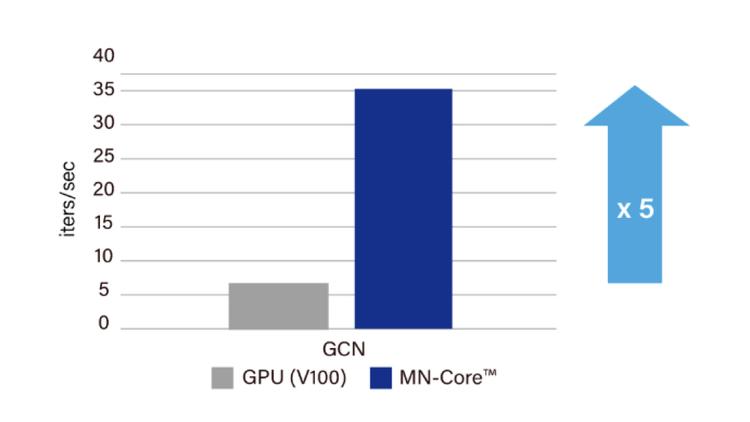

汎用原子レベルシミュレーターMatlantis™のコア技術であるPFP(Preferred Potential)にMN-Coreを活用し、新素材の物性シミュレーションを5倍以上高速化(MN-Core第1世代)

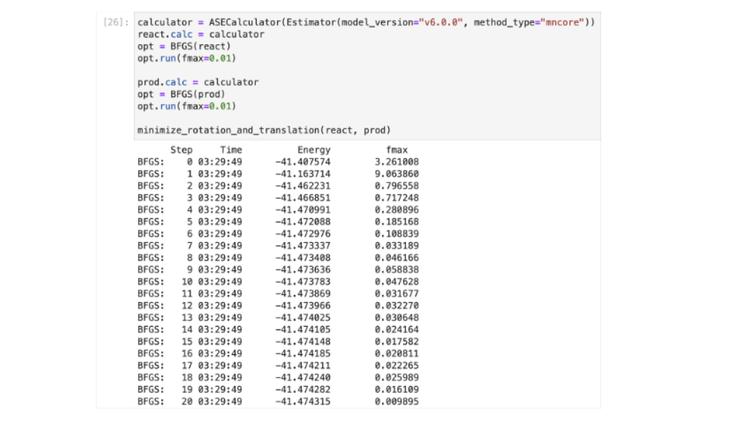

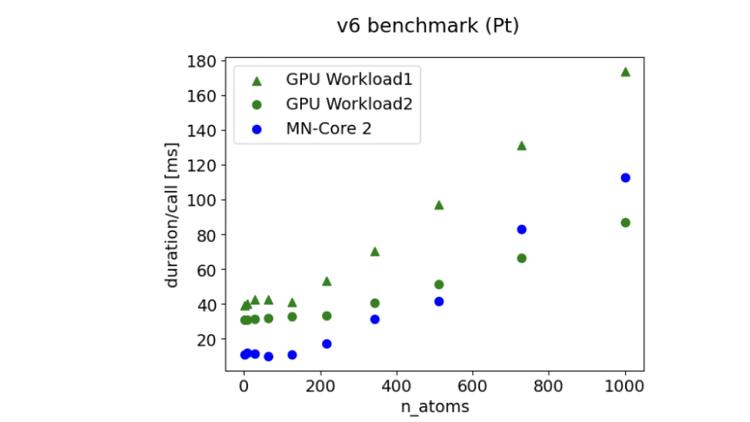

PFNのクラウドサービスPFCP™を通じたMN-Core 2(第2世代)の計算力をMatlantisで試験的に利用、低原子数領域の原子レベルシミュレーションにおいてGPUに対して高速化を確認

PFNはAIの計算資源としての半導体の需要増をいち早く予測し、2016年にAIプロセッサーMN-Coreシリーズ第1世代の開発を開始。現在では開発・製品化を進めています。

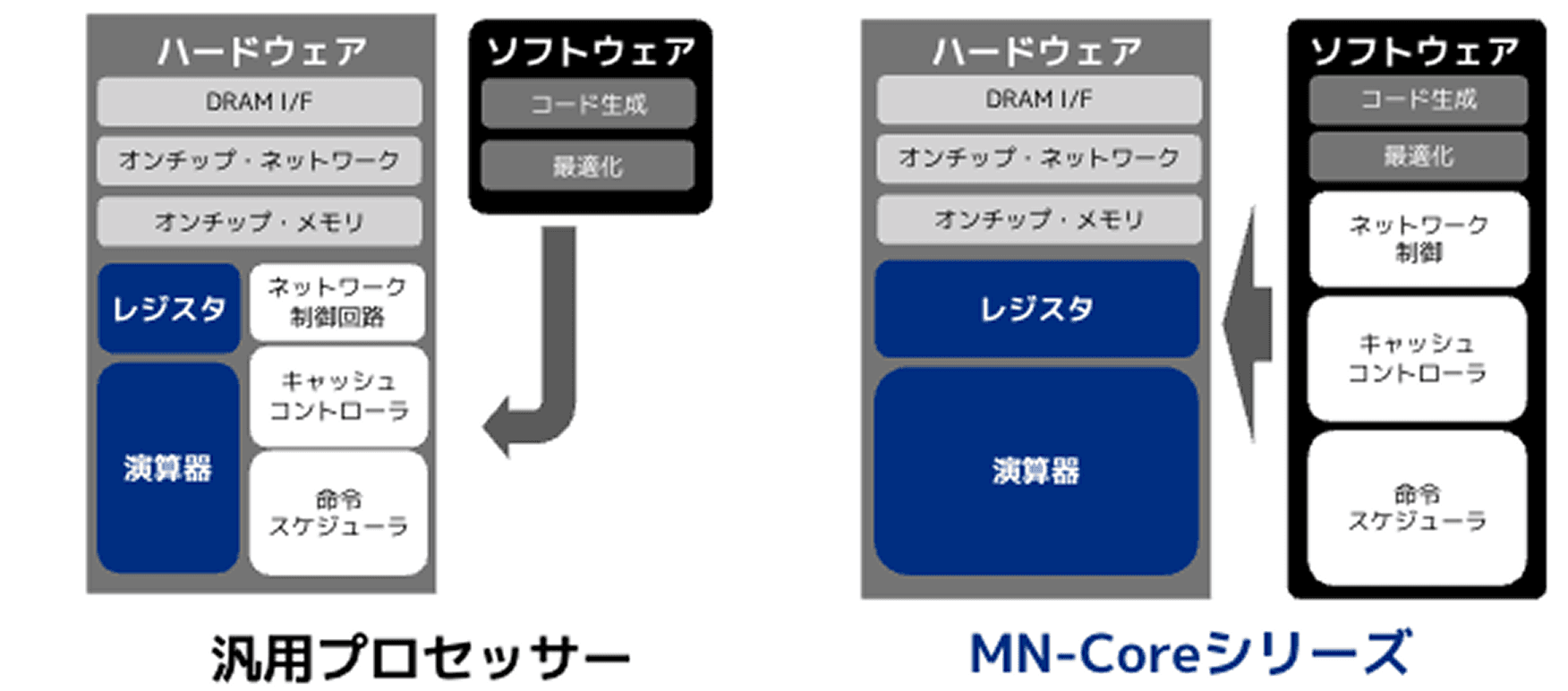

MN-Coreシリーズでは、通常はハードウェアに搭載される制御などの機能をソフトウェアが担うことで、ハードウェアの演算器面積を最大化しました。これにより、高い演算性能と電力効率を実現しています。

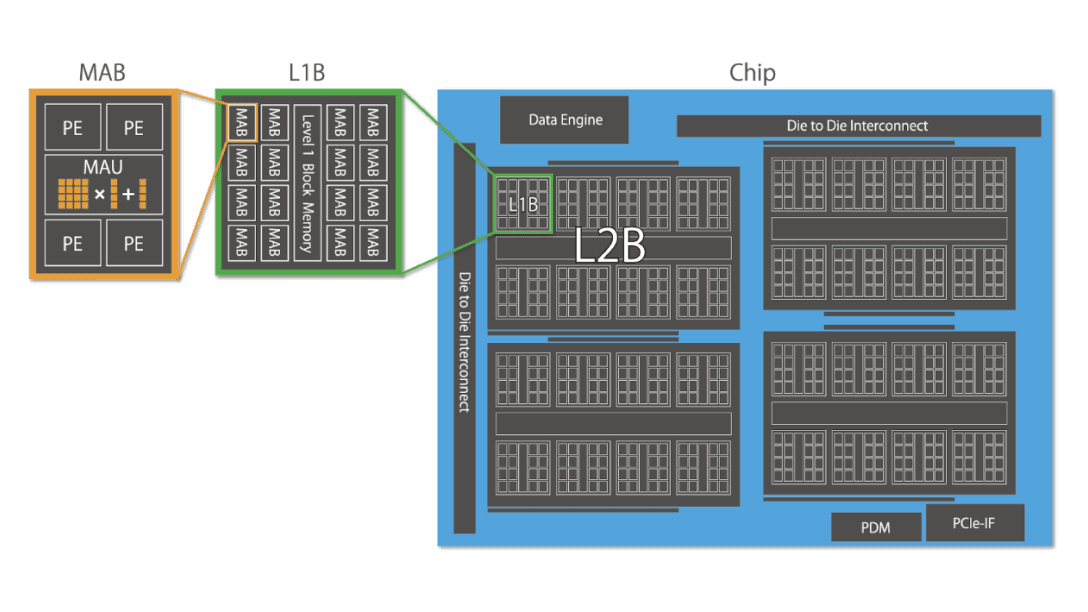

MN-Coreは極めて高密度にハードウェア実装された行列演算器(MAU: Matrix Arithmetic Unit)を持ちます。条件分岐のない完全なSIMD(single instruction, multiple data: 単一命令・複数データ)動作をするシンプルなアーキテクチャを採用することによって、半導体の面積に対して演算器の占める割合を最大化します。MAU(matrix arithmetic unit: 行列演算器)と4つのPEを合わせた行列演算器ブロック(MAB: Matrix Arithmetic Block)は階層的に配置され、階層間でスキャッター、ギャザー、放送、縮約といった複数のモードを持たせることで、柔軟なプログラミングを可能にしています。

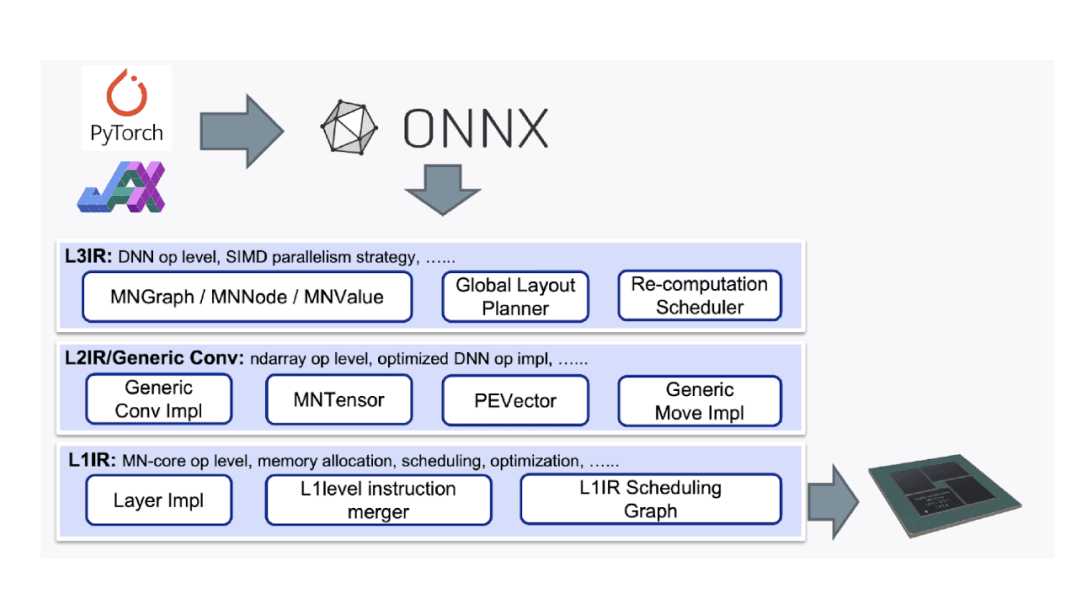

既存のAIワークロードにに大きな改変を加えることなく、スリムかつパワフルに設計されたMN-Coreシリーズプロセッサーの性能を引き出すために、PFNではMN-Coreシリーズ向けコンパイラを独自に開発しています。 MN-Coreシリーズ向けコンパイラはPyTorchやJAXなどの高位言語で定義された計算グラフから最適な命令生成、データ配置、命令供給などを行います。計算グラフレベルの操作から、低レベル命令生成までを最適かつ効率的に行うために、MN-Core向けコンパイラは問題を抽象度に応じて分割し、コンポーネント単位でアルゴリズムの改善が可能な設計を行っています。